#### WISES 07

# Specification for SystemC-AADL interoperability

Eduardo de las Heras Palmero Microelectronic Engineering Group University of Cantabria

#### Outline

- Motivations

- General Concepts

- AADL

- SystemC

- PERFidiX and SCope

- AADL-SystemC Design Flow

- Mapping AADL to SystemC

- Example

#### Motivations

- System design issues:

- Incomplete capture of specification

- Need for design refinement and validation

- Impact of functional and nonfunctional properties until the system integration

- Timing properties

- Software/Hardware co-design

# **AADL Concepts**

#### Architecture Analysis & Design Language

- Standard by the SEI, November 2004

- Graphical and textual Language

- Architecture and model based design

- Precise syntax and semantics

- Specification of Tasks and communications

- Enable analysis and validation of constraints

- Large-scale architectures in a single model

- Incrementally refined

- Analyze the system structure and runtime behavior

# **AADL Concepts**

#### SystemC Concepts

- SystemC features

- Standard platform for system design (IEEE 1666) developed by the OSCI

- -C++ extension

- Strict-time, event driven simulator

- Hierarchical Design

- Concurrent Execution Kernel

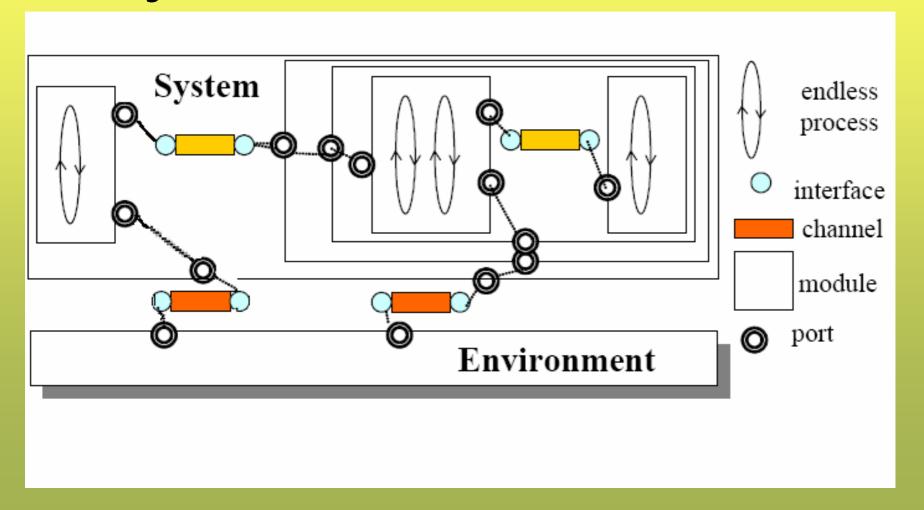

# SystemC Concepts

SystemC Basic Elements

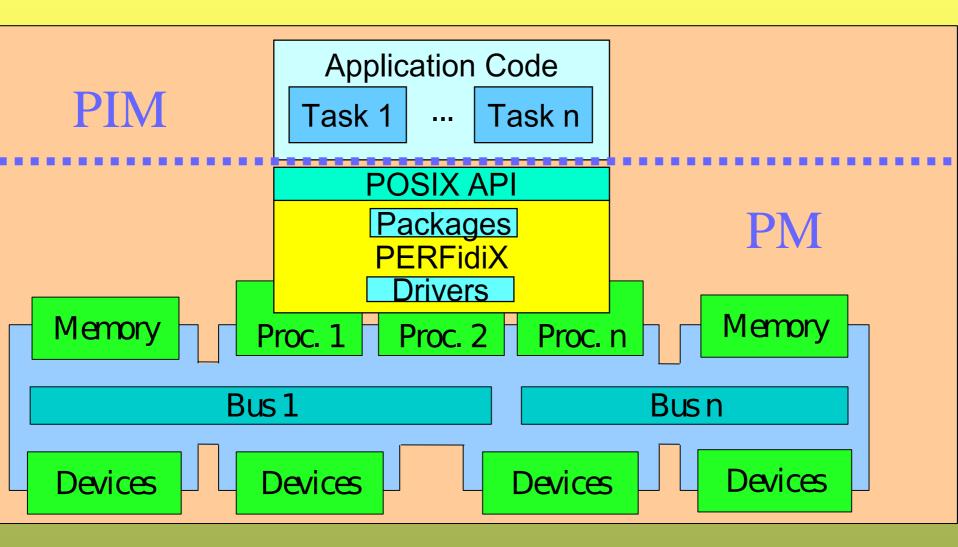

#### **SCope Concepts**

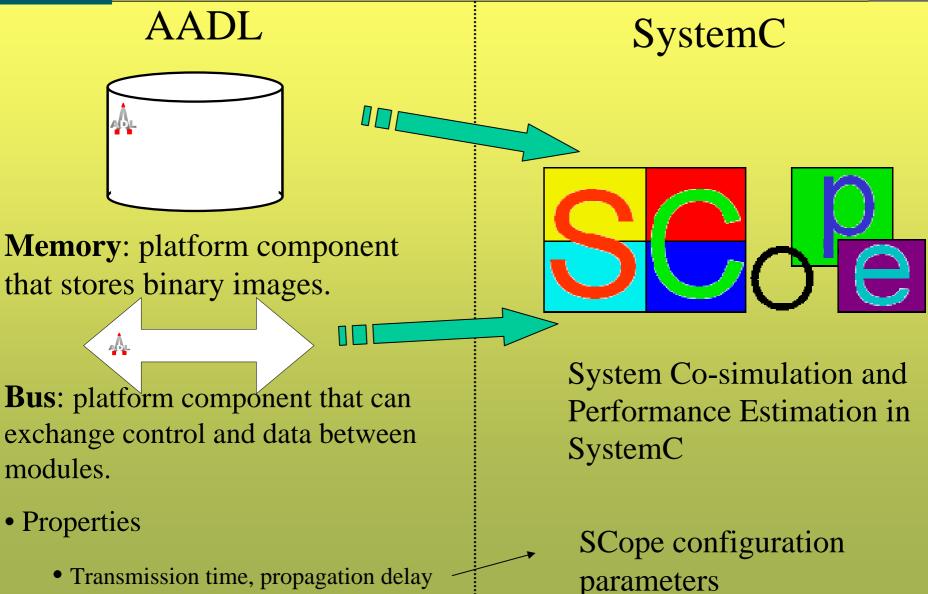

- System Co-simulation and Performance Estimation in SystemC

- Extension of PERFidiX library

- Multi-processor SW source-code simulation

- OS Modelling

- POSIX

- Timed SW simulation

- Performance estimation of SW code

- Time & Power

# **SCope Concepts**

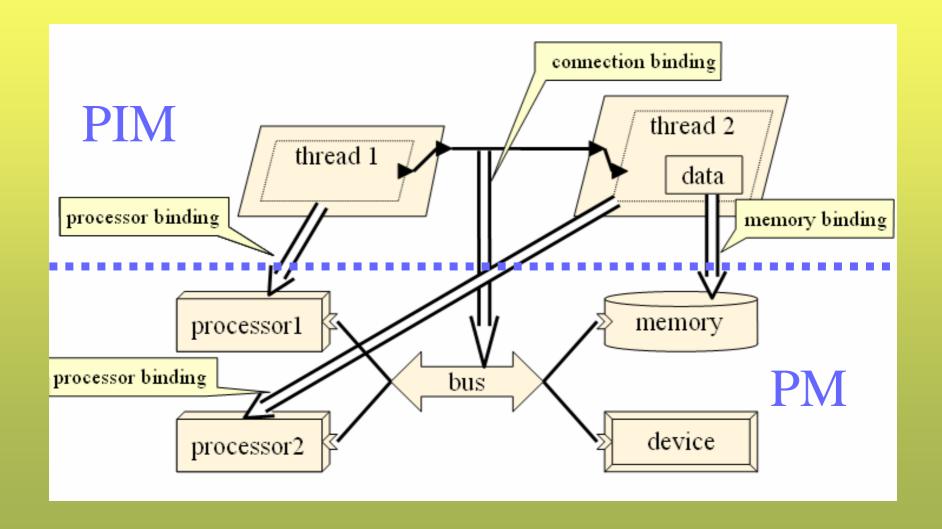

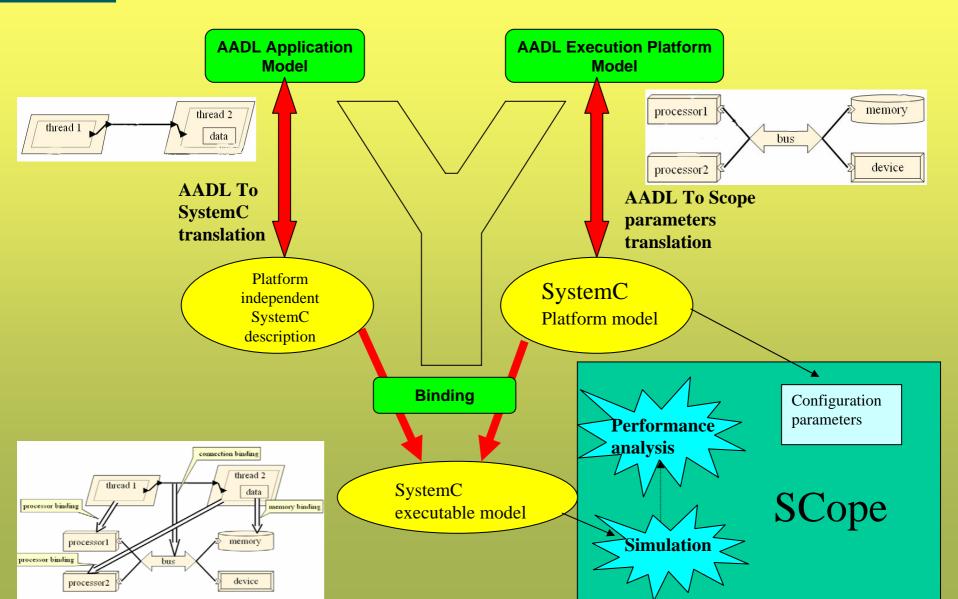

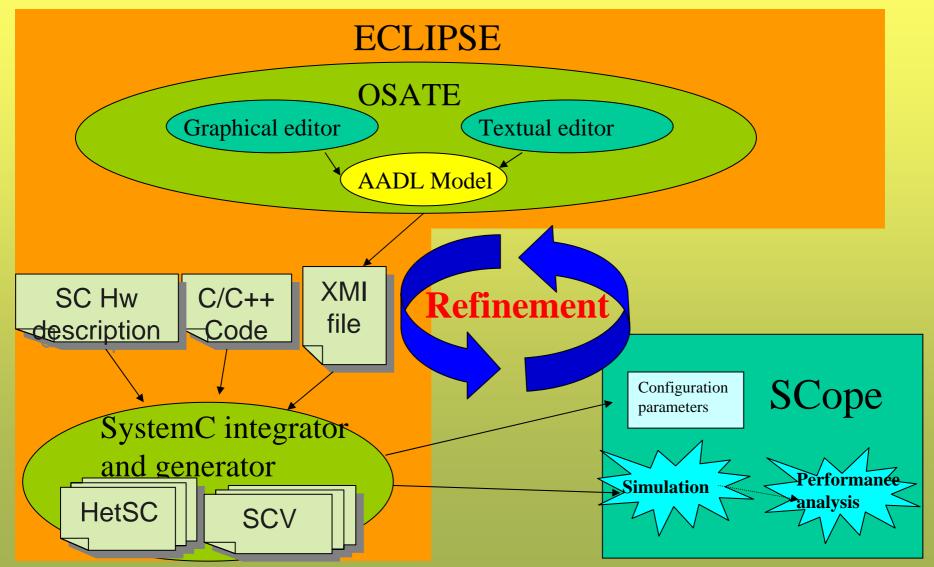

# AADL-SystemC Design Flow

#### AADL to SystemC Framework

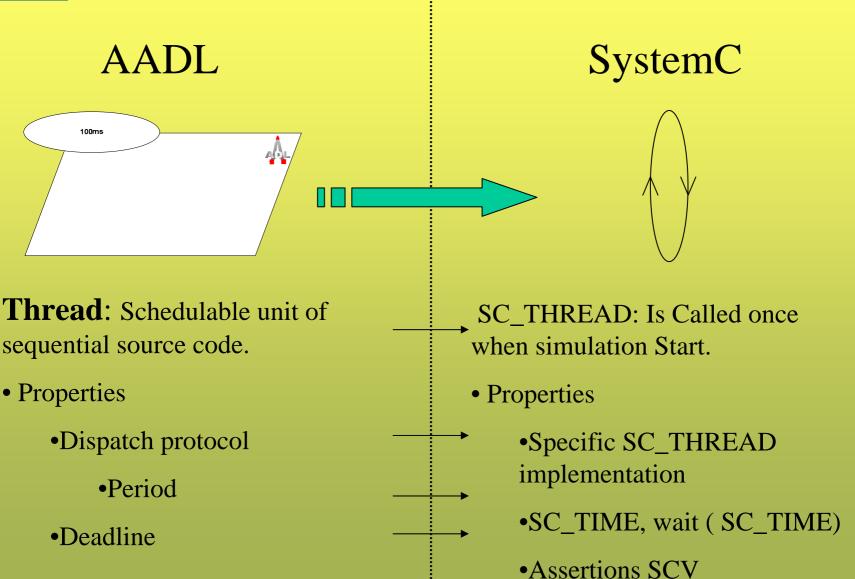

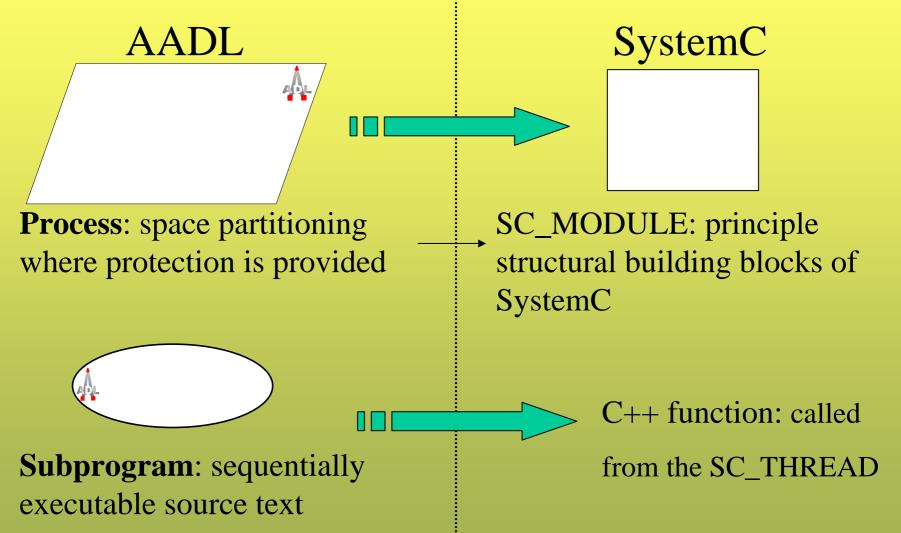

**Data**: Enable manipulate data in—concurrently in non-deterministic order.

- Properties

- Concurrency\_Control\_Protocol

→ Channel: Enable communication between modules

- Properties

- •Semaphores, mutex, custom channels.

**Processor:** Abstraction of hardware and software responsible for scheduling and executing threads.

- Properties

- Process\_Swap\_Execution\_time

- Thread\_Swap\_Execution\_time

- Scheduling\_Protocols

High level, POSIX simulation library and performance Analysis

→ SCope configuration parameters

POSIX scheduling\_protocols

**Devices:** Execution platform component that interface with the exterior

Event data port

Event port

Data port

Data port

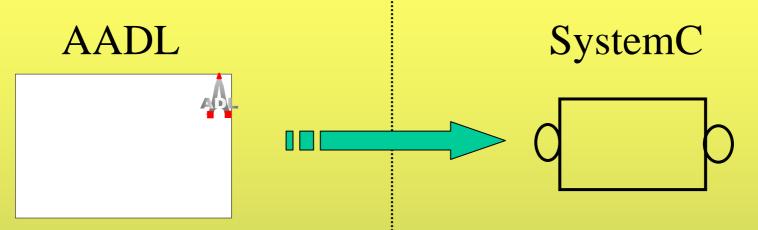

**Ports and Connections:** Logical Connections to exchange control and data between threads.

#### SystemC

SystemC description at various levels:

- •TLM

- •RTL

- Synthesis

Signal channel, ports, interface

FIFO channel ports, interface

Custom Channels, ports, interface

#### **SystemC**

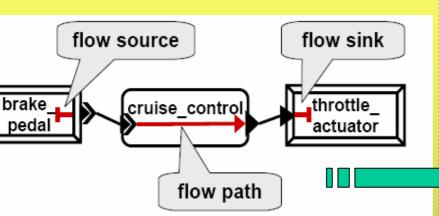

Corresponding access to subcomponents involve in the flow implementation

Flows: support for various forms of flow analysis

- •Flow source

- •Flow path

- •Flow sink

Random generation of tokens using SCV

Implementation of Write and read access method

Data recording for posterior analysis using SCV

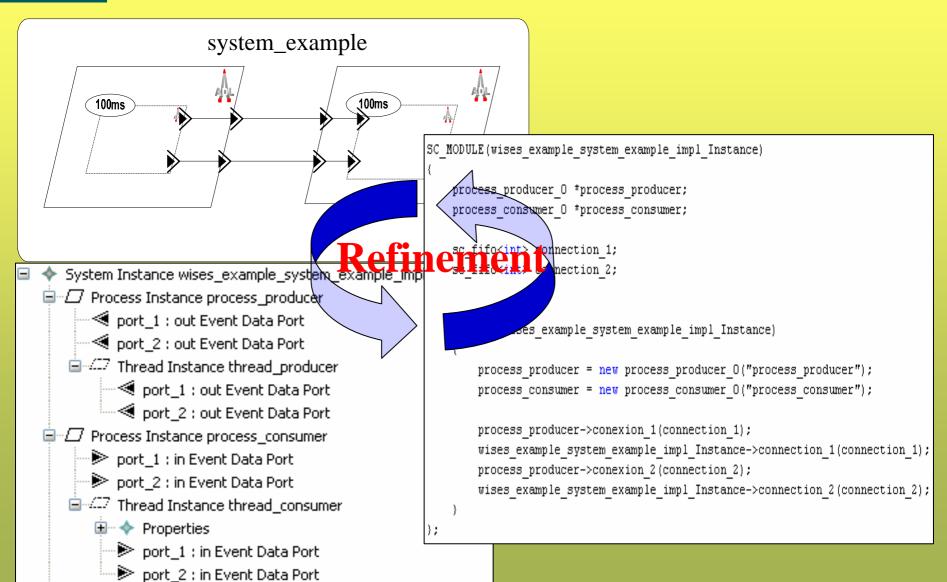

# Example

#### Example

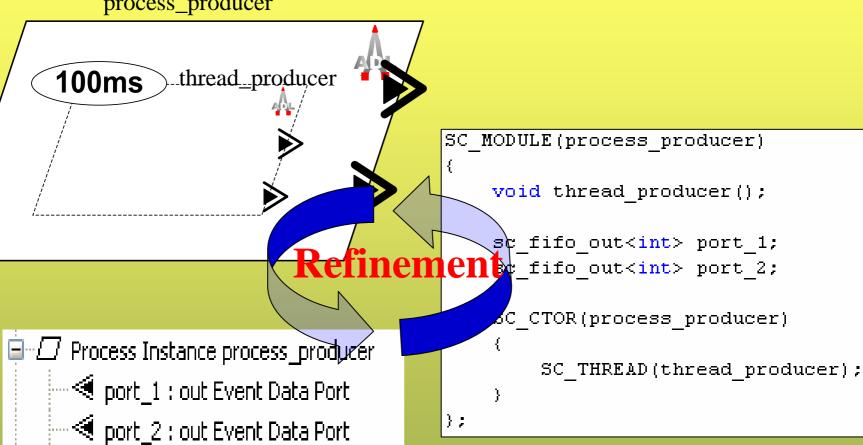

#### process\_producer

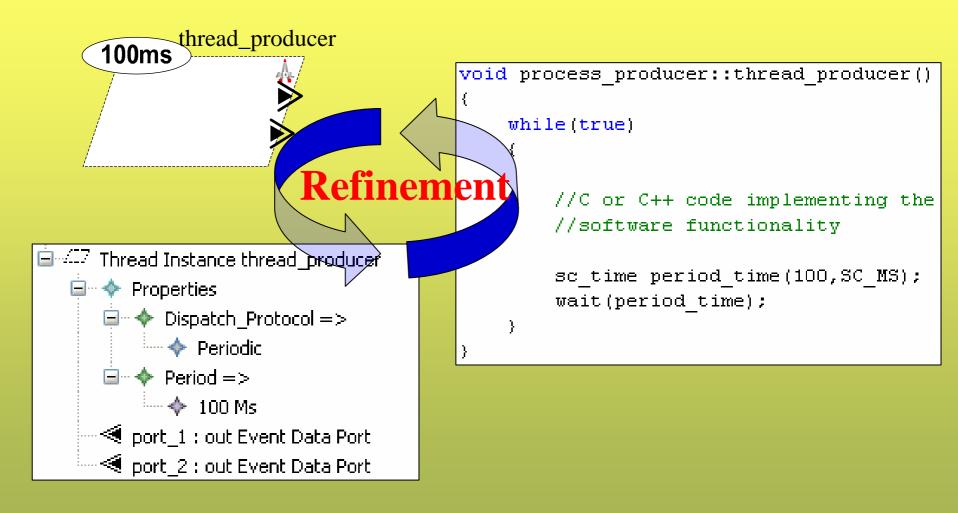

■ 4.7 Thread Instance thread producer.

# Example

#### Conclusions

- SystemC allows modeling AADL

- Different abstraction levels.

- Refinement

- Validation

- Specification for model transformation from AADL to SystemC

- Tool proposal for embedded system design

#### **END**

#### THANK YOU FOR YOUR ATTENTION

QUESTIONS?